CMOS軌到軌放大器電路的問題解決(jue) 方案

從(cong) 數十年前被發明以來,MOS晶體(ti) 管的尺寸已經被大大縮小。門氧化層厚度、通道長度和寬度的降低,推動了整體(ti) 電路尺寸和功耗的大大減少。由於(yu) 門氧化物厚度的減小, 可容許電源電壓降低,而通道長度和寬度的縮減則縮小了產(chan) 品的外形並加快了其速度性能。這些改進推動了高頻率CMOS軌到軌輸入/輸出放大器的性能發展,以滿足當今係統設計者對於(yu) 某種新型模擬電路日益增加的需求,這種電路必須能夠以和數字電路同樣低的電源電壓進行工作。

本應用筆記解答了有關(guan) 一代CMOS軌到軌放大器的一些獨特問題。文章一開始大致討論並講述了傳(chuan) 統電壓反饋和電流反饋放大器電路的拓撲,以及導致反饋放大器振蕩的 常見原因。為(wei) 了方便分析和討論,我們(men) 將CMOS軌到軌放大器電路分成4大塊:輸入、中間增益、輸出和反饋網絡階段。文中將展示每個(ge) 階段受頻率影響的增益和相位移,隨後展示並討論一個(ge) 包含了所有4大基本電路區塊的完整係統仿真。而第二部分則將展示並討論三種用於(yu) 解決(jue) 放大器振蕩問題的使用方案的機製、各方麵的折衷和優(you) 勢。

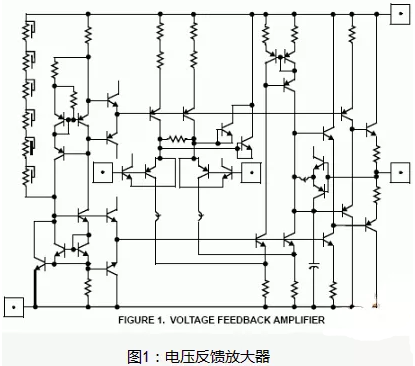

電壓反饋放大器

圖1展示了一個(ge) EL5157的簡化方案 - 這是一款非常流行的高帶寬電壓反饋放大器。這一方案采用一個(ge) 經典的差分輸入階來驅動折疊的Cascode第二階,由第二階在高阻抗增益節點上將輸入階的差分電壓轉換成一個(ge) 電流,該電流隨著放大器的高電壓增益而實現。從(cong) 本質上來講,在高阻抗節點上變成一個(ge) 輸出信號的第二階電流源輸出阻抗會(hui) 增加任何在信號通道晶體(ti) 管內(nei) 產(chan) 生的電流差距。輸出階是一個(ge) 推挽式AB級緩衝(chong) 器,將高電壓增益緩衝(chong) 成放大器的單端輸出。

輸出感應

感應器是一種阻抗受頻率影響的電子元器件:低頻率時其阻抗較低,高頻率時阻抗則升高。“理想的”運算放大器輸出阻抗是零,但在實際中放大器的輸出阻抗是感應式的,就像感應器一樣會(hui) 隨著頻率的增加而增加。圖2展示了EL5157的輸出阻抗。利用運算放大器的應用中所經常遇到的一個(ge) 挑戰,就是驅動一個(ge) 電容性負載。之所以具有挑戰性,是因為(wei) 運算放大器的感應輸出會(hui) 與(yu) 電容性負載聯合生成一個(ge) LC諧振回路拓撲,而在這個(ge) 拓撲中電容性負載會(hui) 與(yu) 感應式驅動阻抗一起,當反饋圍繞回路關(guan) 閉時造成額外的相位滯後。相位餘(yu) 度的縮小有可能導致放大器的振蕩。在振蕩時,放大器會(hui) 變得非常熱,甚至可能自毀。要解決(jue) 這一問題,有多種非常 的方案。

聲明:本網站原創內(nei) 容,如需轉載,請注明出處;本網站轉載的內(nei) 容(文章、圖片、視頻)等資料版權歸原網站所有。如我們(men) 采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯係我們(men) ,以便迅速采取適當處理措施;郵箱:limeijun@transql.com