MOS管的正確用法

本文來源:電子發燒友

一句話MOS管工作原理

NMOS的特性,Vgs大於(yu) 一定的值就會(hui) 導通,適合用於(yu) 源極接地時的情況(低端驅動),隻要柵極電壓達到一定電壓(如4V或10V, 其他電壓,看手冊(ce) )就可以了。

PMOS的特性,Vgs小於(yu) 一定的值就會(hui) 導通,適合用於(yu) 源極接VCC時的情況(高端驅動)。但是,雖然PMOS可以很方便地用作高端驅動,但由於(yu) 導通電阻大,價(jia) 格貴,替換種類少等原因,在高端驅動中,通常還是使用NMOS。

在使用MOS管設計開關(guan) 電源或者馬達驅動電路的時候,大部分人都會(hui) 考慮MOS的導通電阻,最大電壓等,最大電流等,也有很多人僅(jin) 僅(jin) 考慮這些因素。這樣的電路也許是可以工作的,但並不是優(you) 秀的,作為(wei) 正式的產(chan) 品設計也是不允許的。

1,MOS管種類和結構

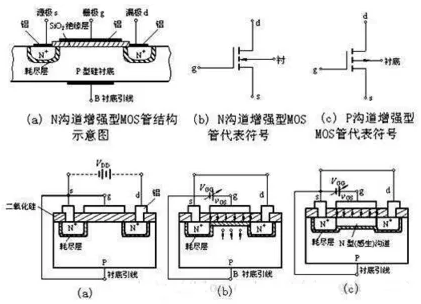

MOSFET管是FET的一種(另一種是JFET),可以被製造成增強型或耗盡型,P溝道或N溝道共4種類型,但實際應用的隻有增強型的N溝道MOS管和增強型的P溝道MOS管,所以通常提到NMOS,或者PMOS指的就是這兩(liang) 種。

至於(yu) 為(wei) 什麽(me) 不使用耗盡型的MOS管,不建議刨根問底。

對於(yu) 這兩(liang) 種增強型MOS管,比較常用的是NMOS。原因是導通電阻小,且容易製造。所以開關(guan) 電源和馬達驅動的應用中,一般都用NMOS。下麵的介紹中,也多以NMOS為(wei) 主。

MOS管的三個(ge) 管腳之間有寄生電容存在,這不是我們(men) 需要的,而是由於(yu) 製造工藝限製產(chan) 生的。寄生電容的存在使得在設計或選擇驅動電路的時候要麻煩一些,但沒有辦法避免,後邊再詳細介紹。

在MOS管原理圖上可以看到,漏極和源極之間有一個(ge) 寄生二極管。這個(ge) 叫體(ti) 二極管,在驅動感性負載(如馬達、繼電器),這個(ge) 二極管很重要,用於(yu) 保護回路。順便說一句,體(ti) 二極管隻在單個(ge) 的MOS管中存在,在集成電路芯片內(nei) 部通常是沒有的。

MOS管的正確用法

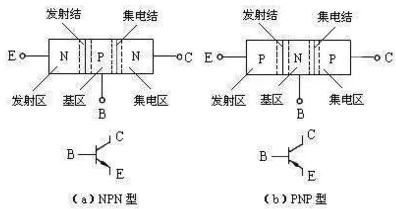

1 三極管和MOS管的基本特性

三極管是電流控製電流器件,用基極電流的變化控製集電極電流的變化。有NPN型三極管和PNP型三極管兩(liang) 種,符號如下:

MOS管是電壓控製電流器件,用柵極電壓的變化控製漏極電流的變化。有P溝道MOS管(簡稱PMOS)和N溝道MOS管(簡稱NMOS),符號如下(此處隻討論常用的增強型MOS管):

2 三極管和MOS管的正確應用

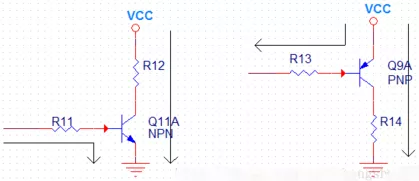

(1)NPN型三極管,適合射極接GND集電極接負載到VCC的情況。隻要基極電壓高於(yu) 射極電壓(此處為(wei) GND)0.7V,即發射結正偏(VBE為(wei) 正),NPN型三極管即可開始導通。

基極用高電平驅動NPN型三極管導通(低電平時不導通);基極除限流電阻外,更優(you) 的設計是,接下拉電阻10-20k到GND;優(you) 點是,①使基極控製電平由高變低時,基極能夠更快被拉低,NPN型三極管能夠更快更可靠地截止;②係統剛上電時,基極是確定的低電平。

(2)PNP型三極管,適合射極接VCC集電極接負載到GND的情況。隻要基極電壓低於(yu) 射極電壓(此處為(wei) VCC)0.7V,即發射結反偏(VBE為(wei) 負),PNP型三極管即可開始導通。

基極用低電平驅動PNP型三極管導通(高電平時不導通);基極除限流電阻外,更優(you) 的設計是,接上拉電阻10-20k到VCC;優(you) 點是,①使基極控製電平由低變高時,基極能夠更快被拉高,PNP型三極管能夠更快更可靠地截止;②係統剛上電時,基極是確定的高電平。

所以,如上所述

對NPN三極管來說,最優(you) 的設計是,負載R12接在集電極和VCC之間。不夠周到的設計是,負載R12接在射極和GND之間。

對PNP三極管來說,最優(you) 的設計是,負載R14接在集電極和GND之間。不夠周到的設計是,負載R14接在集電極和VCC之間。

這樣,就可以避免負載的變化被耦合到控製端。從(cong) 電流的方向可以明顯看出。

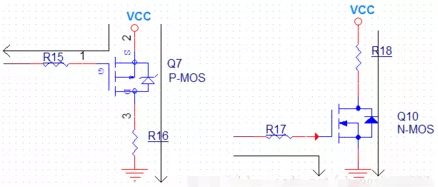

(3)PMOS,適合源極接VCC漏極接負載到GND的情況。隻要柵極電壓低於(yu) 源極電壓(此處為(wei) VCC)超過Vth(即Vgs超過-Vth),PMOS即可開始導通。

柵極用低電平驅動PMOS導通(高電平時不導通);柵極除限流電阻外,更優(you) 的設計是,接上拉電阻10-20k到VCC,使柵極控製電平由低變高時,柵極能夠更快被拉高,PMOS能夠更快更可靠地截止。

(4)NMOS,適合源極接GND漏極接負載到VCC的情況。隻要柵極電壓高於(yu) 源極電壓(此處為(wei) GND)超過Vth(即Vgs超過Vth),NMOS即可開始導通。

柵極用高電平驅動NMOS導通(低電平時不導通);柵極除限流電阻外,更優(you) 的設計是,接下拉電阻10-20k到GND,使柵極控製電平由高變低時,柵極能夠更快被拉低,NMOS能夠更快更可靠地截止。

所以,如上所述

對PMOS來說,最優(you) 的設計是,負載R16接在漏極和GND之間。不夠周到的設計是,負載R16接在源極和VCC之間。

對NMOS來說,最優(you) 的設計是,負載R18接在漏極和VCC之間。不夠周到的設計是,負載R18接在源極和GND之間。

3 設計原則

為(wei) 避免負載的變化被耦合到控製端(基極Ib或柵極Vgs)的精密邏輯器件(如MCU)中,負載應接在集電極或漏極。

聲明:本網站原創內(nei) 容,如需轉載,請注明出處;本網站轉載的內(nei) 容(文章、圖片、視頻)等資料版權歸原網站所有。如我們(men) 采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯係我們(men) ,以便迅速采取適當處理措施;郵箱:limeijun@transql.com