i2c總線協議標準與(yu) 規範

本文來源:電子發燒友

I2C總線協議

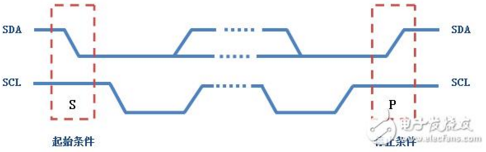

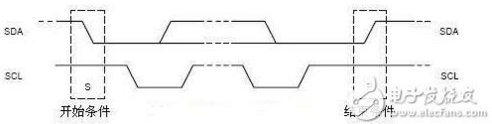

I2C協議規定,總線上數據的傳(chuan) 輸必須以一個(ge) 起始信號作為(wei) 開始條件,以一個(ge) 結束信號作為(wei) 傳(chuan) 輸的停止條件。起始和結束信號總是由主設備產(chan) 生。總線在空閑狀態時,SCL和SDA都保持著高電平,當SCL為(wei) 高電平而SDA由高到低的跳變,表示產(chan) 生一個(ge) 起始條件;當SCL為(wei) 高而SDA由低到高的跳變,表示產(chan) 生一個(ge) 停止條件。在起始條件產(chan) 生後,總線處於(yu) 忙狀態,由本次數據傳(chuan) 輸的主從(cong) 設備獨占,其他I2C器件無法訪問總線;而在停止條件產(chan) 生後,本次數據傳(chuan) 輸的主從(cong) 設備將釋放總線,總線再次處於(yu) 空閑狀態。如圖所示:

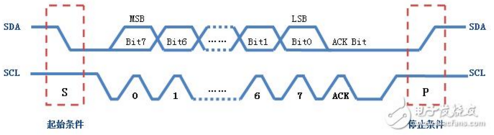

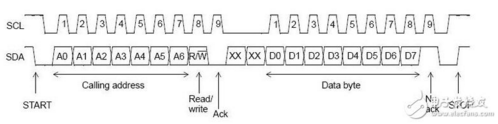

在了解起始條件和停止條件後,我們(men) 再來看看在這個(ge) 過程中數據的傳(chuan) 輸是如何進行的。前麵我們(men) 已經提到過,數據傳(chuan) 輸以字節為(wei) 單位。主設備在SCL線上產(chan) 生每個(ge) 時鍾脈衝(chong) 的過程中將在SDA線上傳(chuan) 輸一個(ge) 數據位,當一個(ge) 字節按數據位從(cong) 高位到低位的順序傳(chuan) 輸完後,緊接著從(cong) 設備將拉低SDA線,回傳(chuan) 給主設備一個(ge) 應答位,此時才認為(wei) 一個(ge) 字節真正的被傳(chuan) 輸完成。當然,並不是所有的字節傳(chuan) 輸都必須有一個(ge) 應答位,比如:當從(cong) 設備不能再接收主設備發送的數據時,從(cong) 設備將回傳(chuan) 一個(ge) 否定應答位。數據傳(chuan) 輸的過程如圖所示:

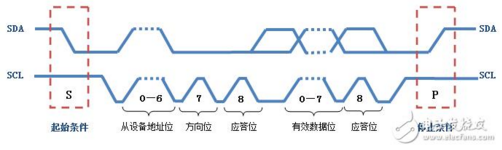

在前麵我們(men) 還提到過,I2C總線上的每一個(ge) 設備都對應一個(ge) 的地址,主從(cong) 設備之間的數據傳(chuan) 輸是建立在地址的基礎上,也就是說,主設備在傳(chuan) 輸有效數據之前要先指定從(cong) 設備的地址,地址指定的過程和上麵數據傳(chuan) 輸的過程一樣,隻不過大多數從(cong) 設備的地址是7位的,然後協議規定再給地址添加一個(ge) 位用來表示接下來數據傳(chuan) 輸的方向,0表示主設備向從(cong) 設備寫(xie) 數據,1表示主設備向從(cong) 設備讀數據。如圖所示:

I2C協議

2條雙向串行線,一條數據線SDA,一條時鍾線SCL。

SDA傳(chuan) 輸數據是大端傳(chuan) 輸,每次傳(chuan) 輸8bit,即一字節。

支持多主控(mulmastering),任何時間點隻能有一個(ge) 主控。

總線上每個(ge) 設備都有自己的一個(ge) addr,共7個(ge) bit,廣播地址全0.

係統中可能有多個(ge) 同種芯片,為(wei) 此addr分為(wei) 固定部分和可編程部份,細節視芯片而定,看datasheet。

1.1 I2C位傳(chuan) 輸

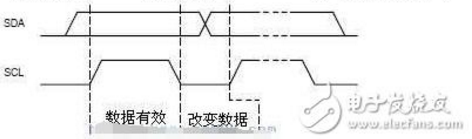

數據傳(chuan) 輸:SCL為(wei) 高電平時,SDA線若保持穩定,那麽(me) SDA上是在傳(chuan) 輸數據bit;若SDA發生跳變,則用來表示一個(ge) 會(hui) 話的開始或結束(後麵講)

數據改變:SCL為(wei) 低電平時,SDA線才能改變傳(chuan) 輸的bit

1.2 I2C開始和結束信號

開始信號:SCL為(wei) 高電平時,SDA由高電平向低電平跳變,開始傳(chuan) 送數據。

結束信號:SCL為(wei) 高電平時,SDA由低電平向高電平跳變,結束傳(chuan) 送數據。

1.3 I2C應答信號

Master每發送完8bit數據後等待Slave的ACK。

即在第9個(ge) clock,若從(cong) IC發ACK,SDA會(hui) 被拉低。

若沒有ACK,SDA會(hui) 被置高,這會(hui) 引起Master發生RESTART或STOP流程,如下所示:

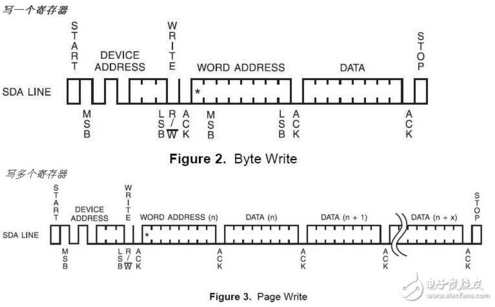

1.4 I2C寫(xie) 流程

寫(xie) 寄存器的標準流程為(wei) :

1. Master發起START

2. Master發送I2C addr(7bit)和w操作0(1bit),等待ACK

3. Slave發送ACK

4. Master發送reg addr(8bit),等待ACK

5. Slave發送ACK

6. Master發送data(8bit),即要寫(xie) 入寄存器中的數據,等待ACK

7. Slave發送ACK

8. 第6步和第7步可以重複多次,即順序寫(xie) 多個(ge) 寄存器

9. Master發起STOP

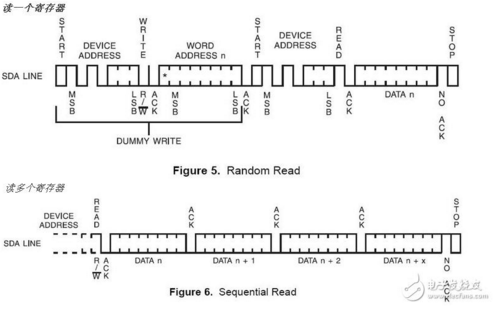

1.5 I2C讀流程

讀寄存器的標準流程為(wei) :

1. Master發送I2C addr(7bit)和w操作1(1bit),等待ACK

2. Slave發送ACK

3. Master發送reg addr(8bit),等待ACK

4. Slave發送ACK

5. Master發起START

6. Master發送I2C addr(7bit)和r操作1(1bit),等待ACK

7. Slave發送ACK

8. Slave發送data(8bit),即寄存器裏的值

9. Master發送ACK

10. 第8步和第9步可以重複多次,即順序讀多個(ge) 寄存器

2. PowerPC的I2C實現

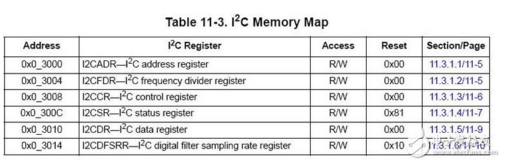

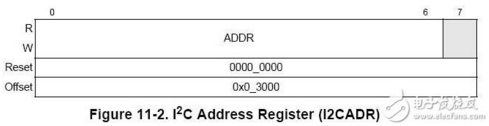

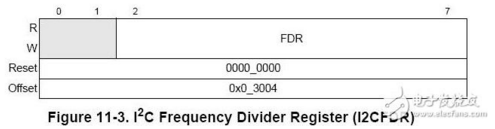

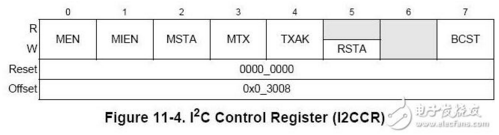

Mpc8560的CCSR中控製I2C的寄存器共有6個(ge) 。

2.1 I2CADR 地址寄存器

CPU也可以是I2C的Slave,CPU的I2C地址有 I2CADR指定

2.2 I2CFDR 頻率設置寄存器

The serial bit clock frequency of SCL is equal to the CCB clock divided by the divider.

用來設置I2C總線頻率

2.3 I2CCR 控製寄存器

MEN: Module Enable. 置1時,I2C模塊使能

MIEN:Module Interrupt Enable. 置1時,I2C中斷使能。

MSTA:Master/slave mode. 1 Master mode,0 Slave mode.

當1-》0時,CPU發起STOP信號

當0-》1時,CPU發起START信號

MTX:Transmit/receive mode select.0 Receive mode,1 Transmit mode

TXAK:Transfer acknowledge. 置1時,CPU在9th clock發送ACK拉低SDA

RSTA:Repeat START. 置1時,CPU發送REPEAT START

BCST:置1,CPU接收廣播信息(信息的slave addr為(wei) 7個(ge) 0)

I2C總線規範

對於(yu) 麵向8位的數字控製應用譬如那些要求用微控製器的要建立一些設計標準

? 一個(ge) 完整的係統通常由至少一個(ge) 微控製器和其他外圍器件例如存儲(chu) 器和I/O擴展器組成

? 係統中不同器件的連接成本必須

? 執行控製功能的係統不要求高速的數據傳(chuan) 輸

? 總的效益由選擇的器件和互連總線結構的種類決(jue) 定

產(chan) 生一個(ge) 滿足這些標準的係統需要一個(ge) 串行的總線結構。盡管串行總線沒有並行總線的數據吞吐能力但它們(men) 隻要很少的配線和IC連接管腳,然而,總線不僅(jin) 僅(jin) 是互連的線還包含係統通訊的所有格式和過程串行總線的器件間通訊。必須有某種形式的協議避免所有混亂(luan) 數據丟(diu) 失和妨礙信息的可能性快速器件必須可以和慢速器件通訊係統必須不能基於(yu) 所連接的器件。否則不可能進行修改或改進應當設計一個(ge) 過程決(jue) 定哪些器件何時可以控製總線。而且如果有不同時鍾速度的器件連接到總線必須定義(yi) 總線的時鍾源所有這些標準都在I2C總線的規範中。

I2C總線的概念

I2C總線支持任何IC生產(chan) 過程(NMOS、CMOS、雙極性)兩(liang) 線。――串行數據SDA和串行時鍾SCL線在連接到總線的器件間傳(chuan) 遞信息,每個(ge) 器件都有一個(ge) 的地址識別無論是微控製器LCD驅動器存儲(chu) 器或鍵盤接口。而且都可以作為(wei) 一個(ge) 發送器或接收器,由器件的功能決(jue) 定很明顯LCD驅動器隻是一個(ge) 接收器而存儲(chu) 器則既可以接收又可以發送數據。除了發送器和接收器外器件在執行數據傳(chuan) 輸時也可以被看作是主機或從(cong) 機。主機是初始化總線的數據傳(chuan) 輸並產(chan) 生允許傳(chuan) 輸的時鍾信號的器件。

聲明:本網站原創內(nei) 容,如需轉載,請注明出處;本網站轉載的內(nei) 容(文章、圖片、視頻)等資料版權歸原網站所有。如我們(men) 采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯係我們(men) ,以便迅速采取適當處理措施;郵箱:limeijun@transql.com