詳解,N溝道MOS管和P溝道MOS管

先講講MOS/CMOS集成電路

MOS集成電路特點:

製造工藝比較簡單、成品率較高、功耗低、組成的邏輯電路比較簡單,集成度高、抗幹擾能力強,特別適合於(yu) 大規模集成電路。

MOS集成電路包括:

NMOS管組成的NMOS電路、PMOS管組成的PMOS電路及由NMOS和PMOS兩(liang) 種管子組成的互補MOS電路,即CMOS電路。

PMOS門電路與(yu) NMOS電路的原理完全相同,隻是電源極性相反而已。

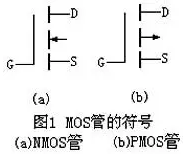

數字電路中MOS集成電路所使用的MOS管均為(wei) 增強型管子,負載常用MOS管作為(wei) 有源負載,這樣不僅(jin) 節省了矽片麵積,而且簡化了工藝利於(yu) 大規模集成。常用的符號如圖1所示。

N溝MOS晶體(ti) 管

金屬-氧化物-半導體(ti) (Metal-Oxide-SemIConductor)結構的晶體(ti) 管簡稱MOS晶體(ti) 管,有P型MOS管和N型MOS管之分。MOS管構成的集成電路稱為(wei) MOS集成電路,而PMOS管和NMOS管共同構成的互補型MOS集成電路即為(wei) CMOS集成電路。

由p型襯底和兩(liang) 個(ge) 高濃度n擴散區構成的MOS管叫作n溝道MOS管,該管導通時在兩(liang) 個(ge) 高濃度n擴散區間形成n型導電溝道。n溝道增強型MOS管必須在柵極上施加正向偏壓,且隻有柵源電壓大於(yu) 閾值電壓時才有導電溝道產(chan) 生的n溝道MOS管。n溝道耗盡型MOS管是指在不加柵壓(柵源電壓為(wei) 零)時,就有導電溝道產(chan) 生的n溝道MOS管。

NMOS集成電路是N溝道MOS電路,NMOS集成電路的輸入阻抗很高,基本上不需要吸收電流,因此,CMOS與(yu) NMOS集成電路連接時不必考慮電流的負載問題。NMOS集成電路大多采用單組正電源供電,並且以5V為(wei) 多。CMOS集成電路隻要選用與(yu) NMOS集成電路相同的電源,就可與(yu) NMOS集成電路直接連接。不過,從(cong) NMOS到CMOS直接連接時,由於(yu) NMOS輸出的高電平低於(yu) CMOS集成電路的輸入高電平,因而需要使用一個(ge) (電位)上拉電阻R,R的取值一般選用2~100KΩ。

N溝道增強型MOS管的結構

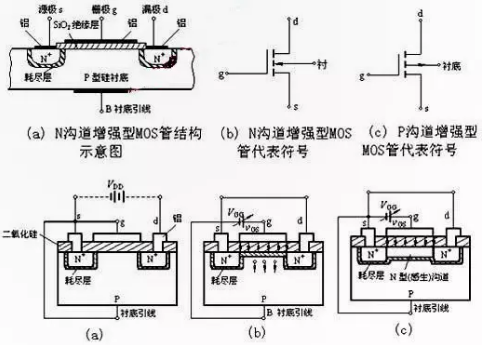

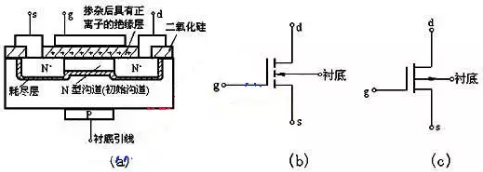

在一塊摻雜濃度較低的P型矽襯底上,製作兩(liang) 個(ge) 高摻雜濃度的N+區,並用金屬鋁引出兩(liang) 個(ge) 電極,分別作漏極d和源極s。

然後在半導體(ti) 表麵覆蓋一層很薄的二氧化矽(SiO2)絕緣層,在漏——源極間的絕緣層上再裝上一個(ge) 鋁電極,作為(wei) 柵極g。

在襯底上也引出一個(ge) 電極B,這就構成了一個(ge) N溝道增強型MOS管。MOS管的源極和襯底通常是接在一起的(大多數管子在出廠前已連接好)。

它的柵極與(yu) 其它電極間是絕緣的。

圖(a)、(b)分別是它的結構示意圖和代表符號。代表符號中的箭頭方向表示由P(襯底)指向N(溝道)。P溝道增強型MOS管的箭頭方向與(yu) 上述相反,如圖(c)所示。

N溝道增強型MOS管的工作原理

(1)vGS對iD及溝道的控製作用

① vGS=0 的情況

從(cong) 圖1(a)可以看出,增強型MOS管的漏極d和源極s之間有兩(liang) 個(ge) 背靠背的PN結。當柵——源電壓vGS=0時,即使加上漏——源電壓vDS,而且不論vDS的極性如何,總有一個(ge) PN結處於(yu) 反偏狀態,漏——源極間沒有導電溝道,所以這時漏極電流iD≈0。

② vGS>0 的情況

若vGS>0,則柵極和襯底之間的SiO2絕緣層中便產(chan) 生一個(ge) 電場。電場方向垂直於(yu) 半導體(ti) 表麵的由柵極指向襯底的電場。這個(ge) 電場能排斥空穴而吸引電子。

排斥空穴:使柵極附近的P型襯底中的空穴被排斥,剩下不能移動的受主離子(負離子),形成耗盡層。吸引電子:將 P型襯底中的電子(少子)被吸引到襯底表麵。

(2)導電溝道的形成:

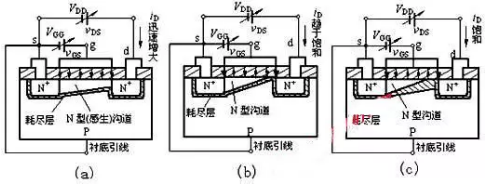

當vGS數值較小,吸引電子的能力不強時,漏——源極之間仍無導電溝道出現,如圖1(b)所示。vGS增加時,吸引到P襯底表麵層的電子就增多,當vGS達到某一數值時,這些電子在柵極附近的P襯底表麵便形成一個(ge) N型薄層,且與(yu) 兩(liang) 個(ge) N+區相連通,在漏——源極間形成N型導電溝道,其導電類型與(yu) P襯底相反,故又稱為(wei) 反型層,如圖1(c)所示。vGS越大,作用於(yu) 半導體(ti) 表麵的電場就越強,吸引到P襯底表麵的電子就越多,導電溝道越厚,溝道電阻越小。

開始形成溝道時的柵——源極電壓稱為(wei) 開啟電壓,用VT表示。

上麵討論的N溝道MOS管在vGS<VT時,不能形成導電溝道,管子處於(yu) 截止狀態。隻有當vGS≥VT時,才有溝道形成。這種必須在vGS≥VT時才能形成導電溝道的MOS管稱為(wei) 增強型MOS管。溝道形成以後,在漏——源極間加上正向電壓vDS,就有漏極電流產(chan) 生。

vDS對iD的影響

如圖(a)所示,當vGS>VT且為(wei) 一確定值時,漏——源電壓vDS對導電溝道及電流iD的影響與(yu) 結型場效應管相似。

漏極電流iD沿溝道產(chan) 生的電壓降使溝道內(nei) 各點與(yu) 柵極間的電壓不再相等,靠近源極一端的電壓最大,這裏溝道最厚,而漏極一端電壓最小,其值為(wei) VGD=vGS-vDS,因而這裏溝道最薄。但當vDS較小(vDS<vGS–VT)時,它對溝道的影響不大,這時隻要vGS一定,溝道電阻幾乎也是一定的,所以iD隨vDS近似呈線性變化。

隨著vDS的增大,靠近漏極的溝道越來越薄,當vDS增加到使VGD=vGS-vDS=VT(或vDS=vGS-VT)時,溝道在漏極一端出現預夾斷,如圖2(b)所示。再繼續增大vDS,夾斷點將向源極方向移動,如圖2(c)所示。由於(yu) vDS的增加部分幾乎全部降落在夾斷區,故iD幾乎不隨vDS增大而增加,管子進入飽和區,iD幾乎僅(jin) 由vGS決(jue) 定。

N溝道增強型MOS管的特性曲線、電流方程及參數

(1)特性曲線和電流方程

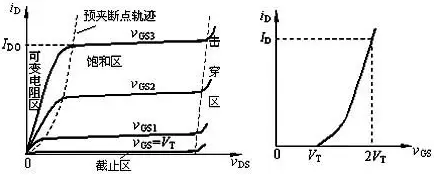

1)輸出特性曲線

N溝道增強型MOS管的輸出特性曲線如圖1(a)所示。與(yu) 結型場效應管一樣,其輸出特性曲線也可分為(wei) 可變電阻區、飽和區、截止區和擊穿區幾部分。

2)轉移特性曲線

轉移特性曲線如圖1(b)所示,由於(yu) 場效應管作放大器件使用時是工作在飽和區(恒流區),此時iD幾乎不隨vDS而變化,即不同的vDS所對應的轉移特性曲線幾乎是重合的,所以可用vDS大於(yu) 某一數值(vDS>vGS-VT)後的一條轉移特性曲線代替飽和區的所有轉移特性曲線。

3)iD與(yu) vGS的近似關(guan) 係

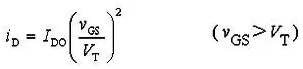

與(yu) 結型場效應管相類似。在飽和區內(nei) ,iD與(yu) vGS的近似關(guan) 係式為(wei)

式中IDO是vGS=2VT時的漏極電流iD。

(2)參數

MOS管的主要參數與(yu) 結型場效應管基本相同,隻是增強型MOS管中不用夾斷電壓VP ,而用開啟電壓VT表征管子的特性。

N溝道耗盡型MOS管的基本結構

(1)結構:

N溝道耗盡型MOS管與(yu) N溝道增強型MOS管基本相似。

(2)區別:

耗盡型MOS管在vGS=0時,漏——源極間已有導電溝道產(chan) 生,而增強型MOS管要在vGS≥VT時才出現導電溝道。

(3)原因:

製造N溝道耗盡型MOS管時,在SiO2絕緣層中摻入了大量的堿金屬正離子Na+或K+(製造P溝道耗盡型MOS管時摻入負離子),如圖1(a)所示,因此即使vGS=0時,在這些正離子產(chan) 生的電場作用下,漏——源極間的P型襯底表麵也能感應生成N溝道(稱為(wei) 初始溝道),隻要加上正向電壓vDS,就有電流iD。

如果加上正的vGS,柵極與(yu) N溝道間的電場將在溝道中吸引來更多的電子,溝道加寬,溝道電阻變小,iD增大。反之vGS為(wei) 負時,溝道中感應的電子減少,溝道變窄,溝道電阻變大,iD減小。當vGS負向增加到某一數值時,導電溝道消失,iD趨於(yu) 零,管子截止,故稱為(wei) 耗盡型。溝道消失時的柵-源電壓稱為(wei) 夾斷電壓,仍用VP表示。與(yu) N溝道結型場效應管相同,N溝道耗盡型MOS管的夾斷電壓VP也為(wei) 負值,但是,前者隻能在vGS<0的情況下工作。而後者在vGS=0,vGS>0,VP<vGS<0的情況下均能實現對iD的控製,而且仍能保持柵——源極間有很大的絕緣電阻,使柵極電流為(wei) 零。這是耗盡型MOS管的一個(ge) 重要特點。圖(b)、(c)分別是N溝道和P溝道耗盡型MOS管的代表符號。

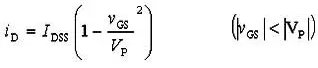

(4)電流方程:

在飽和區內(nei) ,耗盡型MOS管的電流方程與(yu) 結型場效應管的電流方程相同,即:

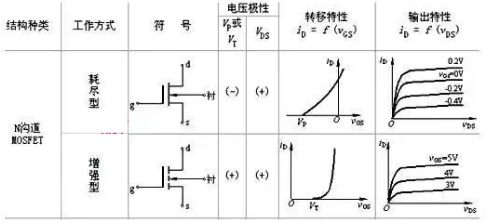

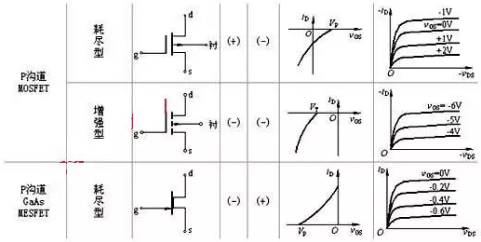

各種場效應管特性比較

P溝MOS晶體(ti) 管

金屬氧化物半導體(ti) 場效應(MOS)晶體(ti) 管可分為(wei) N溝道與(yu) P溝道兩(liang) 大類,P溝道矽MOS場效應晶體(ti) 管在N型矽襯底上有兩(liang) 個(ge) P+區,分別叫做源極和漏極,兩(liang) 極之間不通導,柵極上加有足夠的正電壓(源極接地)時,柵極下的N型矽表麵呈現P型反型層,成為(wei) 連接源極和漏極的溝道。改變柵壓可以改變溝道中的電子密度,從(cong) 而改變溝道的電阻。這種MOS場效應晶體(ti) 管稱為(wei) P溝道增強型場效應晶體(ti) 管。如果N型矽襯底表麵不加柵壓就已存在P型反型層溝道,加上適當的偏壓,可使溝道的電阻增大或減小。這樣的MOS場效應晶體(ti) 管稱為(wei) P溝道耗盡型場效應晶體(ti) 管。統稱為(wei) PMOS晶體(ti) 管。

P溝道MOS晶體(ti) 管的空穴遷移率低,因而在MOS晶體(ti) 管的幾何尺寸和工作電壓絕對值相等的情況下,PMOS晶體(ti) 管的跨導小於(yu) N溝道MOS晶體(ti) 管。此外,P溝道MOS晶體(ti) 管閾值電壓的絕對值一般偏高,要求有較高的工作電壓。它的供電電源的電壓大小和極性,與(yu) 雙極型晶體(ti) 管——晶體(ti) 管邏輯電路不兼容。PMOS因邏輯擺幅大,充電放電過程長,加之器件跨導小,所以工作速度更低,在NMOS電路(見N溝道金屬—氧化物—半導體(ti) 集成電路)出現之後,多數已為(wei) NMOS電路所取代。隻是,因PMOS電路工藝簡單,價(jia) 格便宜,有些中規模和小規模數字控製電路仍采用PMOS電路技術。

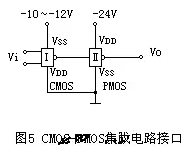

PMOS集成電路是一種適合在低速、低頻領域內(nei) 應用的器件。PMOS集成電路采用-24V電壓供電。如圖5所示的CMOS-PMOS接口電路采用兩(liang) 種電源供電。采用直接接口方式,一般CMOS的電源電壓選擇在10~12V就能滿足PMOS對輸入電平的要求。

MOS場效應晶體(ti) 管具有很高的輸入阻抗,在電路中便於(yu) 直接耦合,容易製成規模大的集成電路。

各種場效應管特性比較

聲明:本網站原創內(nei) 容,如需轉載,請注明出處;本網站轉載的內(nei) 容(文章、圖片、視頻)等資料版權歸原網站所有。如我們(men) 采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯係我們(men) ,以便迅速采取適當處理措施;郵箱:limeijun@transql.com